Designing Solder Mask Opening Compensation to Offset Exposure-Development Dimensional Deviation

1. Sources of Dimensional Deviation

-

Exposure tool accuracy: OptICal distortion (±5μm) and alignment errors.

-

Photoresist properties: Shrinkage (0.1–0.3%) and swelling during development.

-

Development process: Temperature (±1°C) and pressure (±0.1 bar) variations.

-

Solder mask flow: Thickness non-uniformity (CV>5%) causing edge retraction (±3–8μm).

2. Compensation Design Methodology

2.1 Experimental Modeling

-

DOE (Design of Experiments): Analyze key factors (line width, spacing, ink thickness).

Example:Design (μm) Exposure (mJ/cm²) Develop (s) Actual (μm) Deviation (μm) 100 120 60 103 +3 100 150 60 98 -2 -

Regression analysis: Derive compensation formula, e.g.,

�comp=�design−(0.15×InkThickness+0.05×DevelopTime).

2.2 Zone-Specific Compensation

-

Center-edge compensation: Add 2–3μm to edge openings due to thermal gradient.

-

Dense area compensation: Use nonlinear models (e.g., quadratic) for pitches <100μm.

2.3 Dynamic Adjustment

-

Real-time feedback: AOI + PID control for adaptive compensation.

-

Compensation mapping: Historical data-driven per-pixel adjustment.

3. Key Parameters & Validation

-

Compensation range: ±5μm (based on Cpk≥1.33).

-

Validation steps:

-

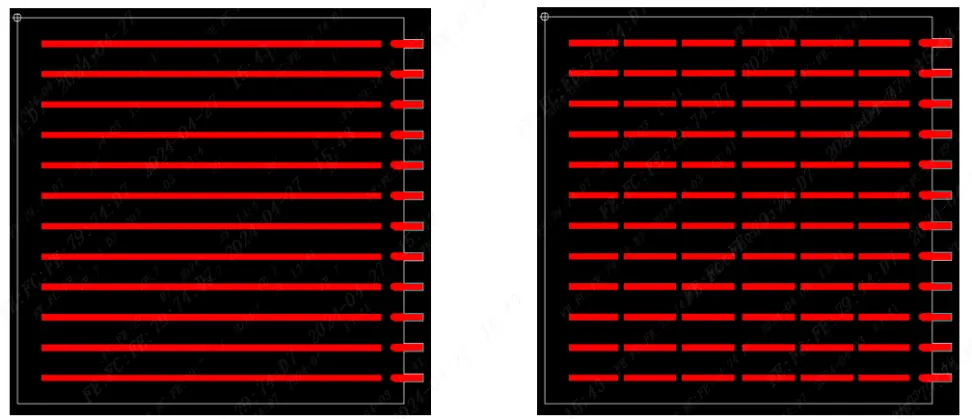

Test patterns: Include stepwise line widths (50–200μm) and grids.

-

Process: Standard LDI exposure (150mJ/cm²) + Na₂CO₃ development (1%).

-

Metrology: Laser confocal microscopy (±0.1μm) or 3D-AOI.

-

Model calibration: Iterate until deviation <±2μm (6σ).

-

4. Process Control

-

Photoresist selection: Low-shrinkage materials (e.g., TMMF S2030, <0.1%).

-

Development optimization:

-

Temperature: 30±0.5°C

-

Spray angle: 30°, coverage ≥120%

-

-

Curing profile: Stepwise heating (80°C→150°C→180°C) to minimize stress.

5. Case Studies & Results

-

Case 1: High-frequency PCB (75μm line)

-

Compensation: Design=73μm (-2μm)

-

Result: 74.8±0.5μm, Cpk=2.0

-

-

Case 2: HDI blind via (50μm opening)

-

Dynamic compensation: Adjusted by real-time conductivity (±1μm)

-

Result: Yield increased from 92% to 98%

-

PCB

PCB FPC

FPC Rigid-Flex

Rigid-Flex FR-4

FR-4 HDI PCB

HDI PCB Rogers High-Frequency Board

Rogers High-Frequency Board PTFE Teflon High-Frequency Board

PTFE Teflon High-Frequency Board Aluminum

Aluminum Copper Core

Copper Core PCB Assembly

PCB Assembly LED light PCBA

LED light PCBA Memory PCBA

Memory PCBA Power Supply PCBA

Power Supply PCBA New Energey PCBA

New Energey PCBA Communication PCBA

Communication PCBA Industrial Control PCBA

Industrial Control PCBA Medical Equipment PCBA

Medical Equipment PCBA PCBA Testing Service

PCBA Testing Service Certification Application

Certification Application RoHS Certification Application

RoHS Certification Application REACH Certification Application

REACH Certification Application CE Certification Application

CE Certification Application FCC Certification Application

FCC Certification Application CQC Certification Application

CQC Certification Application UL Certification Application

UL Certification Application Transformers, Inductors

Transformers, Inductors High Frequency Transformers

High Frequency Transformers Low Frequency Transformers

Low Frequency Transformers High Power Transformers

High Power Transformers Conversion Transformers

Conversion Transformers Sealed Transformers

Sealed Transformers Ring Transformers

Ring Transformers Inductors

Inductors Wires,Cables Customized

Wires,Cables Customized Network Cables

Network Cables Power Cords

Power Cords Antenna Cables

Antenna Cables Coaxial Cables

Coaxial Cables Net Position Indicator

Net Position Indicator Solar AIS net position indicator

Solar AIS net position indicator Capacitors

Capacitors Connectors

Connectors Diodes

Diodes Embedded Processors & Controllers

Embedded Processors & Controllers Digital Signal Processors (DSP/DSC)

Digital Signal Processors (DSP/DSC) Microcontrollers (MCU/MPU/SOC)

Microcontrollers (MCU/MPU/SOC) Programmable Logic Device(CPLD/FPGA)

Programmable Logic Device(CPLD/FPGA) Communication Modules/IoT

Communication Modules/IoT Resistors

Resistors Through Hole Resistors

Through Hole Resistors Resistor Networks, Arrays

Resistor Networks, Arrays Potentiometers,Variable Resistors

Potentiometers,Variable Resistors Aluminum Case,Porcelain Tube Resistance

Aluminum Case,Porcelain Tube Resistance Current Sense Resistors,Shunt Resistors

Current Sense Resistors,Shunt Resistors Switches

Switches Transistors

Transistors Power Modules

Power Modules Isolated Power Modules

Isolated Power Modules DC-AC Module(Inverter)

DC-AC Module(Inverter) RF and Wireless

RF and Wireless